AZ.1.1.2 计算机系统

计算机系统

存储程序式架构

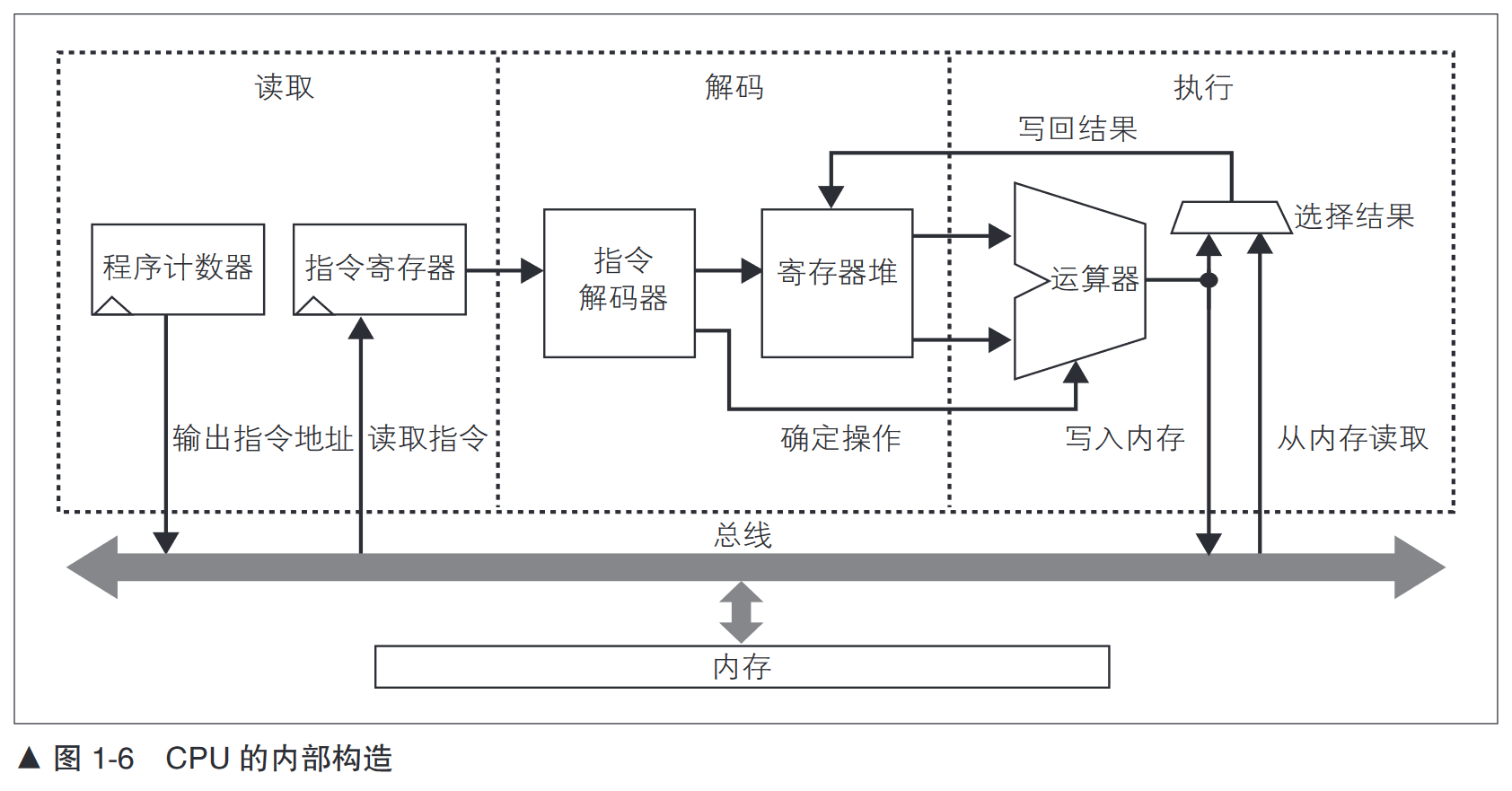

CPU的存储程序式架构 => Stored-program Computer

运行逻辑

- Fetch

- 【Program Counter 寄存器】(即将执行的指令地址)

内存 - 内存

对应地址的指令

- 【Program Counter 寄存器】(即将执行的指令地址)

- Decode

- 【指令解码器】 :解码

- 【General Purpose Register】(通用寄存器):保存地址和运算结果

- Run

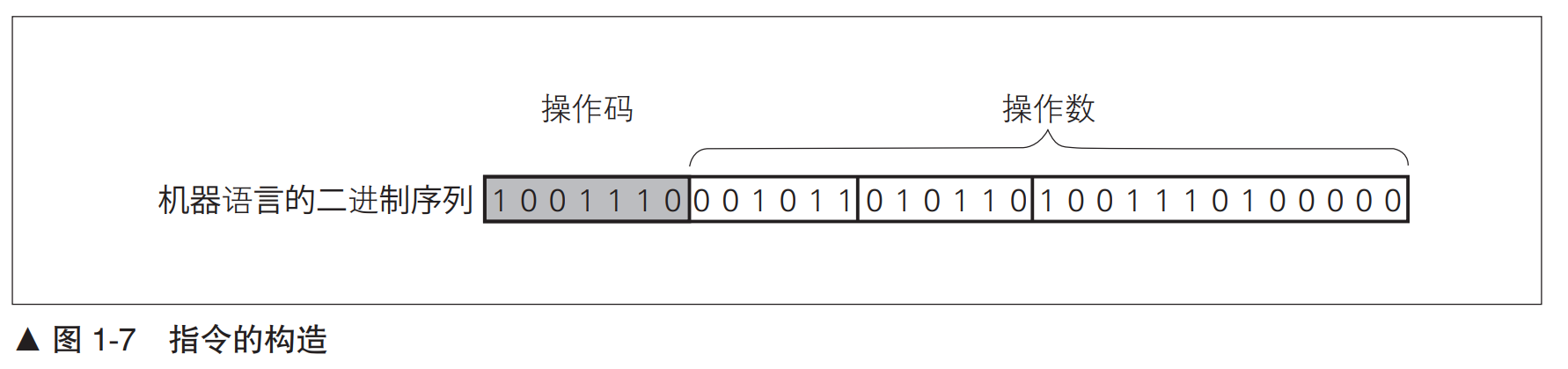

指令

构成

二进制序列:机器语言,包含

- 操作码

- 操作数(数量、位宽根据 CPU 和指令而不同)

- 寄存器地址

- 内存地址

- 立即数:固定常数

按照 操作数数量 划分:1、2、3 操作数形式

按照 指令特征 划分

- Reduced Instruction Set Computer / RISC

- 载入存储架构 Load/Store Architecture :只使用载入和存储指令访问内存,运算指令只能对寄存器中的数据进行操作

- Complex Instruction Set Computer / CISC

位宽

CPU 可以访问的地址空间或数据大小。Eg. 32bit:

划分形式没有明确定义:寄存器或地址的宽度 / 指令或总线的宽度 / CPU 可以处理的整数型数据的宽度(普遍)

字 word:CPU 的字长和位宽通常一致

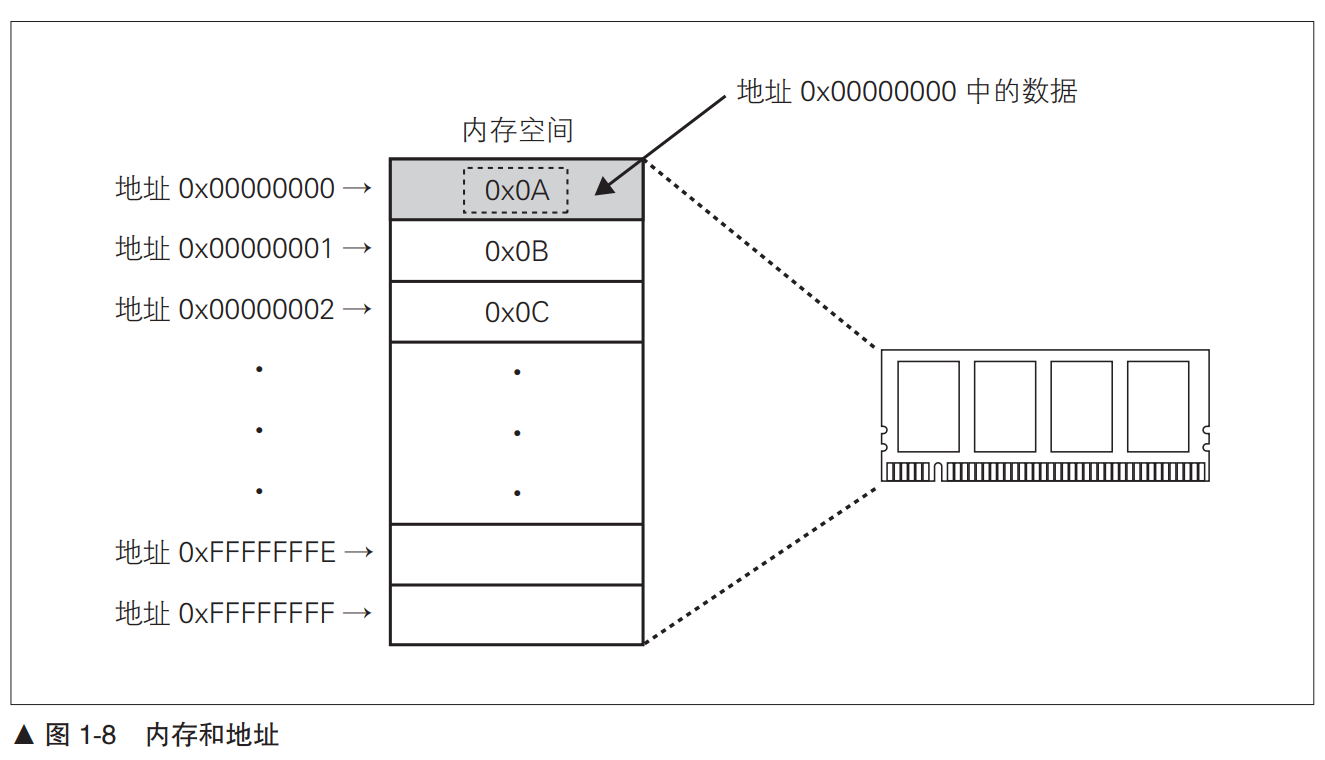

内存

存放运行时指令(程序)和数据的存储器(短期)。 AKA 主存 Main memory。

DRAM 技术 - 动态随机存储器 Dynamic Random Access Memory

电容器中积蓄电荷表示 0/1

由于衰减,需要定期重写:刷新 Refresh

- DRAM种类

- SDRAM 同步DRAM SynchronousDRAM

- DDR SDRAM 双倍速率DRAM Double Data Rate SDRAM

地址

数据的存储位置。大多数数据单元为一字节(8 位)即:字节编址

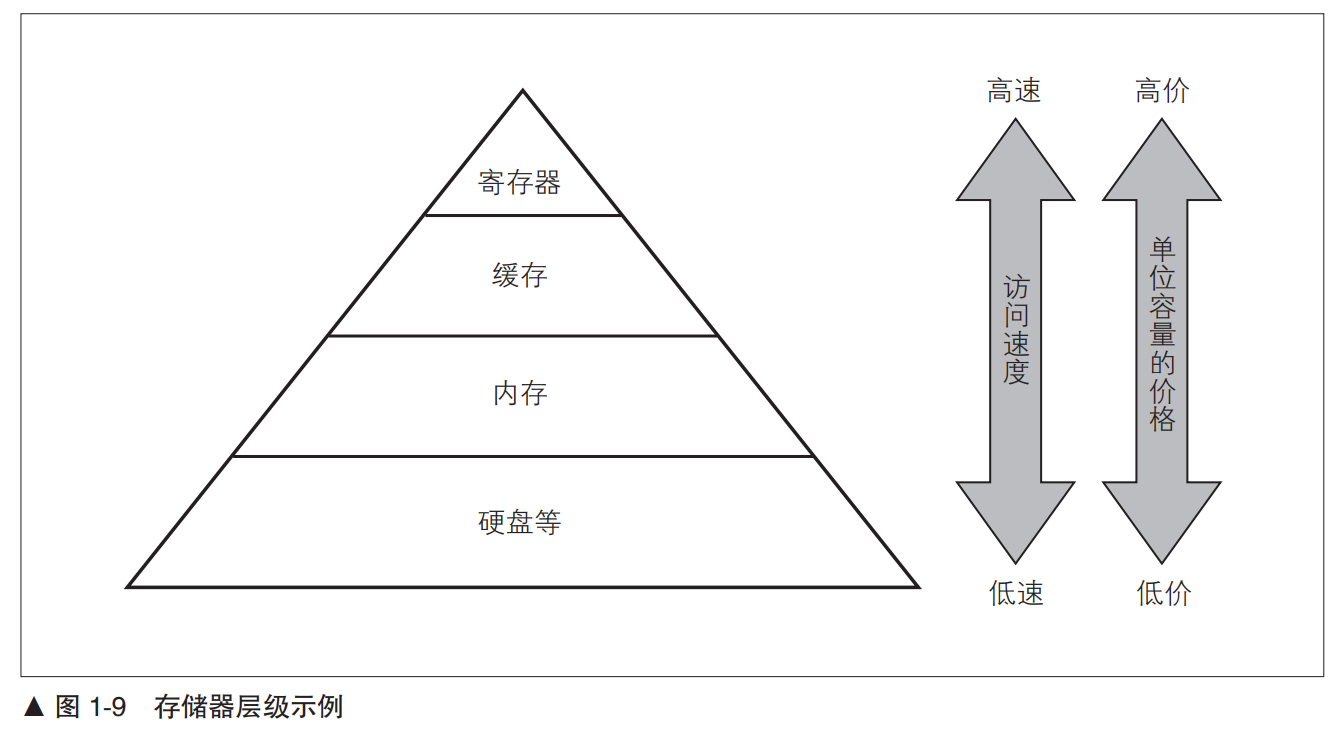

存储器层级

寄存器

速度最快,效率高

缓存

高速,小容量,提高内存的访问速度

根据容量和速度不同,分为一级缓存、二级缓存

内存

硬盘等

I/O Input/Output

进行数据输入输出的装置。

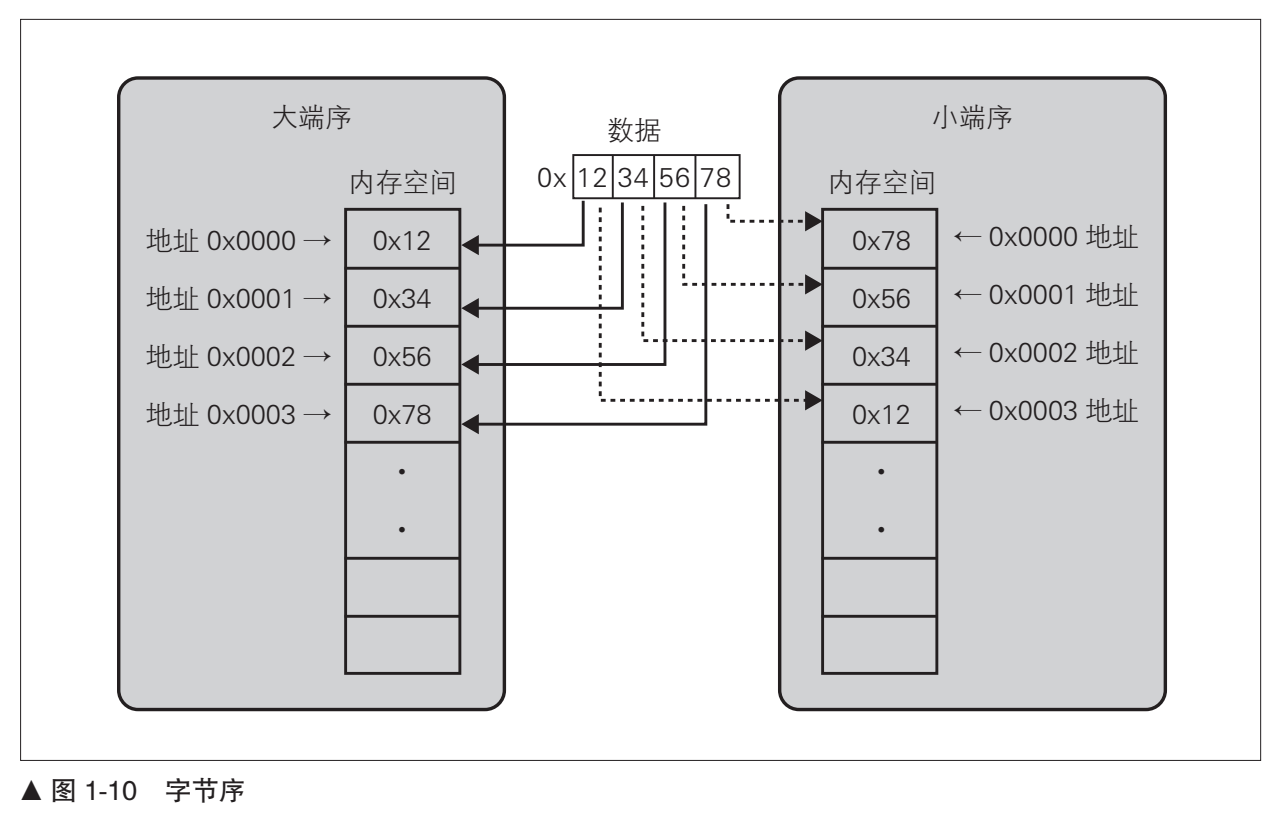

字节序

各个字节的存储顺序

大端序

Eg. SPARC, MIPS

便于人类读取

0x12345678 = 0x12 0x34 0x56 0x78

小端序

Eg. x86

便于机器操作,例如,不同长度数据的低位位置相同,最低位操作不需要寻址到末端,加法可以按照地址顺序传递

0x12345678 = 0x78 0x56 0x34 0x12

双端序

可以依据程序切换

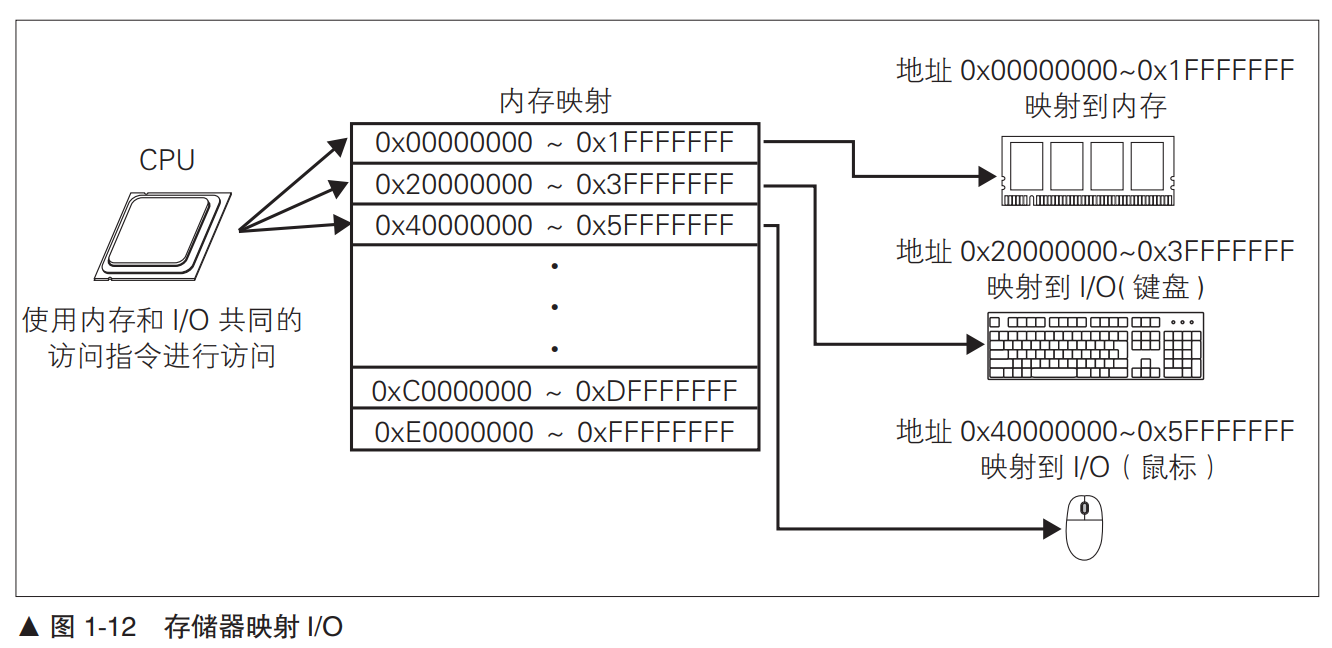

访问 I/O

存储器映射 I/O

- 采用地址管理

- 使用访问内存的指令访问 I/O

- 硬件简单

- 缺点: I/O 占用地址空间

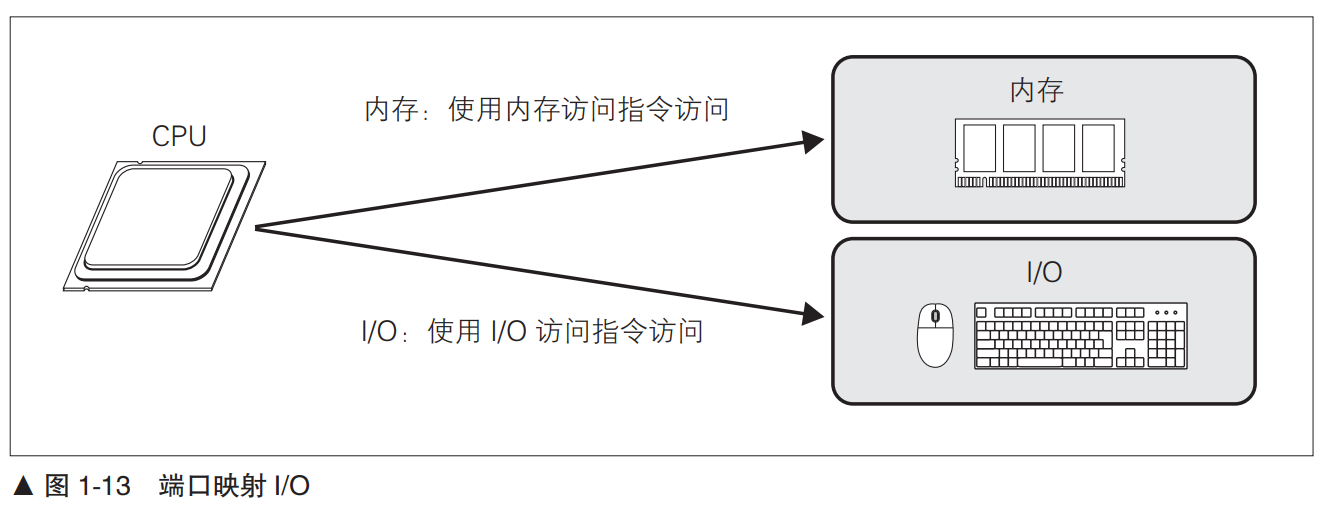

端口映射 I/O

- CPU 专用指令访问 I/O

- 地址空间可以全部分配到内存

- 内存和 I/O 的访问可以在指令级别区分

- 缺点: 硬件设计复杂

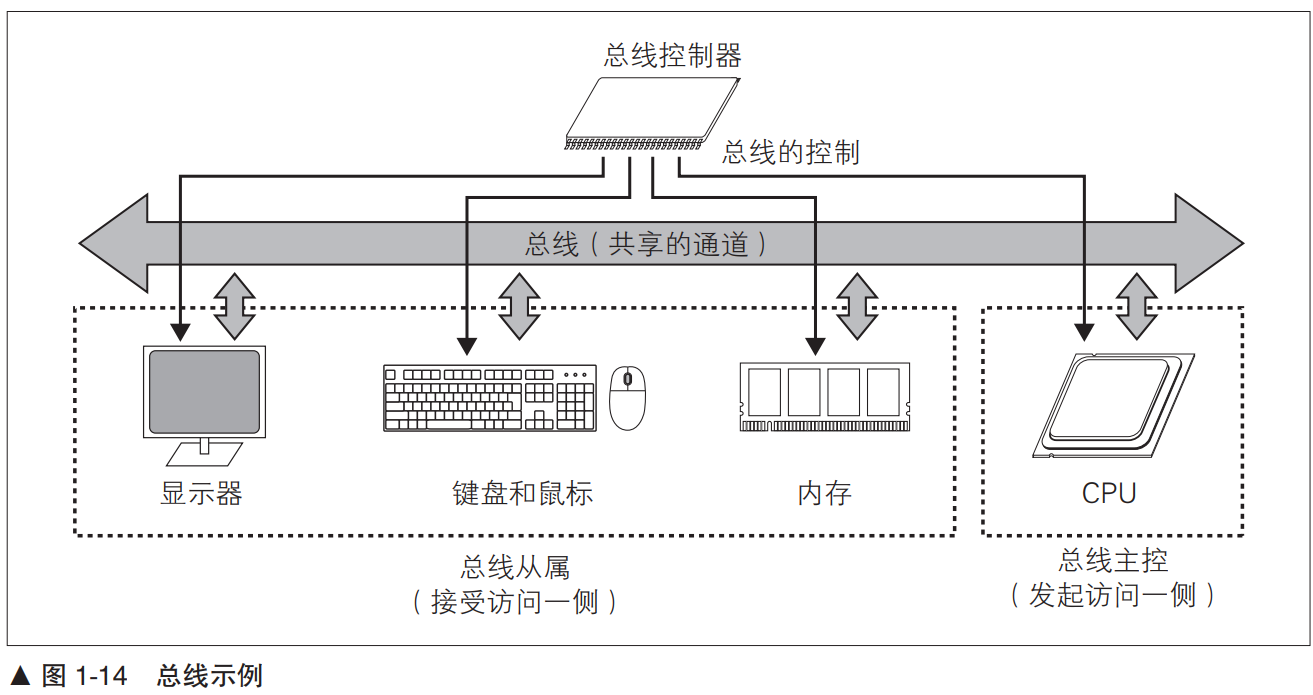

总线

CPU、内存和 I/O 之间交换数据的共同通道

- 总线主控:发起访问的一侧

- 总线从属:接受访问的一侧

总线示例

- 数据总线

- 地址总线

- 控制总线:总线访问的控制

- 总线协议:各个信号的时序,进行交换的规则

- 总线传输:总线交换数据的整个过程

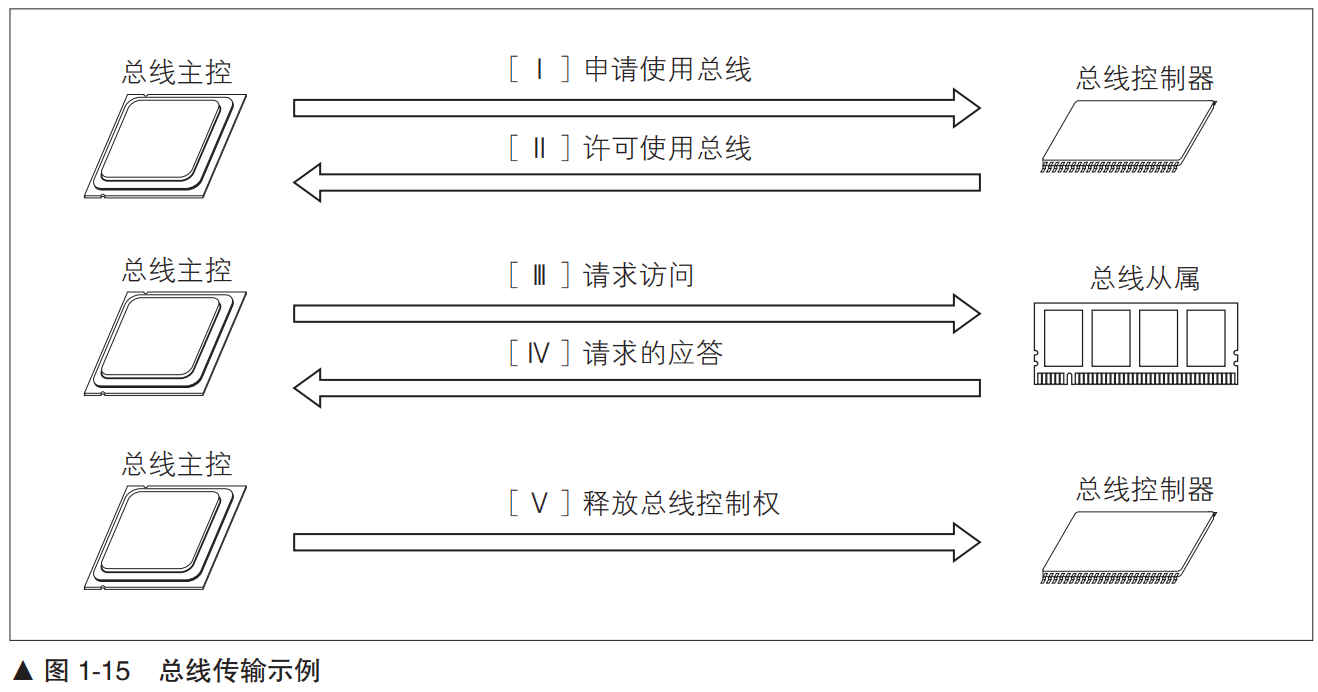

过程

1.申请使用总线

总线主控在访问总线之前先向总线控制器申请总线控制权。

- 总线控制权:访问总线的权利

- 总线仲裁:对多个主线总控的使用进行调停

- 仲裁器:位于总线控制器内,进行总线仲裁

2.许可使用你总线

总线控制器对请求调停,依据仲裁规则进行许可授权。

3.请求访问

获取总线控制权的总线主控对总线从属发送访问请求。请求中包含“要访问哪个地址”、“是读取访问还是写入访问”和“写入时的数据”等信息。

- 片选信号 Chip select

由于总线是共享的通道,总线主控输出的信号会发送到所有总线从属。因此使用片选信号(Chip select,芯片选择信号)等控制信号来区别对哪个从属进行访问。

每个总线从属都设有片选信号,可以使用片选信号选择要访问的总线从属。

一般的总线结构会为每个总线从属分配地址空间。总线控制器内的地址解码器根据要访问的地址产生片选信号。

4.请求的应答

接受访问的总线从属会根据请求对总线主控进行应答。针对请求,应答时采用 Ready 等控制信号。在接受读取请求时,应答的同时输出读出的数据。

5.释放总线控制权

总线主控通知总线控制器释放总线控制权。

优缺点

优点:只要遵循总线协议,任何设备都可以简单地进行连接。使用的是共享通道,硬件的成本也比较低。缺点:吞吐量低。